- #Modelsim tutorial video how to

- #Modelsim tutorial video software license

- #Modelsim tutorial video install

- #Modelsim tutorial video update

- #Modelsim tutorial video pro

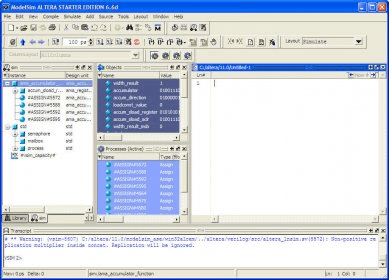

All user interface operations can be scripted and simulations can run in batch or interactive modes. You can edit, recompile, and resimulate without leaving the ModelSim environment. For example, selecting a design region in the Structure window automatically updates the Source, Signals, Process, and Variables windows.

#Modelsim tutorial video update

All windows update automatically following activity in any other window. The graphical user interface is powerful, consistent, and intuitive. Its architecture allows platform-independent compile with the outstanding performance of native compiled code. ModelSim’s award-winning Single Kernel Simulator (SKS) technology enables transparent mixing of VHDL and Verilog in one design. Wa_cq_url: "/content/In addition to supporting standard HDLs, ModelSim DE increases design quality and debug productivity. Wa_audience: "emtaudience:business/btssbusinesstechnologysolutionspecialist/developer/fpgaengineer", Secretive tool on converting your text, audio and graphic banner to video. Create a banner image as a visual for the video. Text-To-Audio Creation using the most realistic Text-to-speech technology tool. Final output sample and tutorial on creating new text from existing text. Wa_english_title: "ModelSim*\u002DIntel® FPGA Edition Software", Welcome to the course: The Ultimate Text-To-Video Creation. Wa_subject: "emtsubject:itinformationtechnology/enterprisecomputing/programmablelogic", Wa_emtsubject: "emtsubject:itinformationtechnology/enterprisecomputing/programmablelogic", (6) state machine (6) testbench (6) block RAM (5) file handling (5) synthesisable (5) fixed point package (4) port mapping (4) video tutorials (4) arrays and records (3). Wa_emttechnology: "emttechnology:inteltechnologies/intelfpgatechnologies", You should get the following waveform when you simulate the codes correctly. Wa_emtcontenttype: "emtcontenttype:donotuse/webpage/landingpage", Make a copy of your Quartus project and Qsys system from exercise 4 and make a new Qsys project inside: add the following IP using the IP Catalog on the left (use the search box to find them more easily). Instances from our pre-compiled libraries do not count towards the 3,000 instance limitation. Use ModelSim to verify the output frequency and amplitude. Note: ModelSim*-Intel® FPGA edition software supports designs of up to 3,000 instances. (Including Intel® MAX® CPLDs, Intel® Arria®, Intel® Cyclone®, and Intel® Stratix® series Intel® FPGAs)

#Modelsim tutorial video pro

Intel® Quartus® Prime lite edition, standard edition, and pro edition software

The adder inputs (, ab) are 3-bit signals, while its output (sum) is a 4-bit signal, so overflow never occurs. The cir cuit used in the tutorial is the registered unsigned adder of figure A.1a, synthesized with the VHDL code of figure A.1b. Intel® Quartus® Prime Design Software support This tutorial is based on Vivado HLx 2018.2 WebPACKfree at xilinx(.com). Every 12 months you must regenerate your license file in the Self-Service Licensing Center to renew your license for the specific ModelSim*-Intel® FPGA edition software version that you purchased. Modelsim 8.1 download Modelsim 6. When the lock detects the correct input sequence, it will set its output high for one clock cycle as a sign to unlock.

#Modelsim tutorial video how to

You will learn the steps in the standard FPGA design flow, how to use Intel Altera’s Quartus Prime Development Suite to create a pipelined multiplier, and how to verify the integrity of the design using the RTL Viewer and by simulation using ModelSim. The example used in this tutorial is a simple design describing an electronic lock that can be unlocked by entering a 4-digit PIN (4169) code from a key pad.

#Modelsim tutorial video install

But they all look and feel the same, and they are sufficient, even for advanced VHDL. The files watch.edf and watch.srr, Chapter 1 Synplify/ ModelSim Tutorial for. In Module 2 you will install and use sophisticated FPGA design tools to create an example design. All free ModelSim versions are speed-restricted in some way. That’s why you will find many installation options for ModelSim on this list.

In addition to supporting standard HDLs, ModelSim DE increases design quality and debug productivity.

#Modelsim tutorial video software license

The ModelSim*-Intel® FPGA edition software license expires 12 months after the date of purchase. ModelSim / QuestaSim, produced by Siemens EDA (formerly Mentor Graphics), is one of the most popular HDL simulators. ModelSim DE packs an unprecedented level of verification capabilities in a cost-effective HDL simulation solution. Note: The ModelSim*-Intel® FPGA edition software requires a valid license. $1,995 includes software updates for one year

0 kommentar(er)

0 kommentar(er)